Sega Technical Overview 1.00

GENESIS Technical Overview

# CONFIDENTIAL

PROPERTY OF SEGA

#### GENESIS:

```

68000 @8 MHz

• main CPU

• 1 MByte (8 Mbit) ROM Area

• 64 KByte RAM Area

VDP (Video Display Processor)

dedicated video display processor

controls playfield & sprites

- capable of DMA

- Horizontal & Vertical interrupts

• 64 KBytes of dedicated VRAM (Video Ram)

• 64 x 9-bits of CRAM (Color RAM)

z80 @4 MHz

• controls PSG (Programmable Sound Generator) & FM Chips

• 8 KBytes of dedicated Sound Ram

VIDEO:

• NOTE: Playfield and Sprites are character-based

• Display Area (visual)

- 40 chars wide x 28 chars high

each char is 8 x 8 pixels

pixel resolution = 320 x 224

- 3 Planes

• 2 scrolling playfields

• 1 sprite plane

• definable priorities between planes

- Playfields:

• 6 different sizes

• 1 playfield can have a "fixed" window

• playfield map

- each char position takes 2 Bytes, that includes:

• char name (10 bits); points to char definition

• horizontal flip

• vertical flip

```

- color palette (2 bits); index into CRAM

- priority

- scrolling: - 1 pixel scrolling resolution

- horizontal:

- whole playfield as unit

- each character line

- each scan line

- vertical:

- whole playfield as unit2 char wide columns

- Sprites:

- 1 x 1 char up to 4 x 4 chars

- up to 80 sprites can be defined

- up to 20 sprites displayed on a scan line

- sprite priorities

- Character Definitions4 bits/pixel; points to color register

- 4 bytes/scanline of char

- 32 bytes for complete char definition

- playfield & sprite chars are the same!

# COLOR:

- Uses CRAM (part of the VDP)

64 9-bit wide color registers

64 colors out of 512 possible colors

- 3 bits of Red

- 3 bits of Green

- 3 bits of Blue

- 4 palettes of 16 colors

- Oth color (of each palette) is always transparent

### OTHER:

#### - DMA

- removes the 68000 from the BUS

- can move 205 Bytes/scanline during VBLANK

- there are 36 scanlines during VBLANK

DMA can move 7380 Bytes during VBLANK

- Horizontal & Vertical interrupts

## SOUND:

- Z80 controls: PSG (TI 76489 chip)

- FM chip (Yamaha YM 2612)

- 6-channel stereo

- Z80 can access ROM data 8 KBytes RAM

# HARDWARE:

- 2 controllers

- joypad 3 buttons

- Start button

- 1 external port2 video-outs (RF & RGB)

- audio jack (stereo)

volume control (for audio jack)

# \*\*\*\*\*\* INDEX \*\*\*\*\*\*

| 1. | MEMORY MAP                                                                                                                                    | 1                                      |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|    | § 1 MEGA DRIVE 16BIT MODE 1                                                                                                                   |                                        |

|    | _ 68000 MEMORY MAP<br>_ Z80 MEMORY MAP<br>_ 68000 ACCESS TO Z80 MEMORY<br>_ I/O AREA<br>_ CONTROL AREA<br>_ VDP AREA                          | 1<br>2<br>2<br>3<br>3<br>4             |

| 2. | <b>VDP 315-5313</b><br>(Video Display Processor)                                                                                              | 5                                      |

|    | _ TERMINOLOGY                                                                                                                                 | 6                                      |

|    | § 1 DISPLAY SPECIFICATION 7                                                                                                                   |                                        |

|    | <pre>§ 2 VDP STRUCTURE 9 _ CTRL _ VRAM _ CRAM _ VSRAM _ DMA</pre>                                                                             | 9<br>9<br>9<br>9<br>9                  |

|    | <pre>\$ 3 INTERRUPTS 10 _ VERTICAL INTERRUPT _ HORIZONTAL INTERRUPT _ EXTERNAL INTERRUPT</pre>                                                | 10<br>10<br>11                         |

|    | <pre>\$ 4 VDP INTERFACE 12     _ \$C00000 (DATA CHANNEL)     \$C00004 (CONTROL CHANNEL)     \$C00008 (HV COUNTER)</pre>                       | 13<br>13<br>15                         |

|    | <b>§ 5 VDP REGISTER</b> 15<br>Reg. # 0 - Reg. # 3<br>Reg. # 4 - Reg. #10<br>Reg. #11 - Reg. #14<br>Reg. #15 - Reg. #18<br>Reg. #19 - Reg. #23 | 16<br>17<br>18<br>19<br>20             |

|    | <pre>\$ 6 ACCESS VDP RAM</pre>                                                                                                                | 21<br>21<br>22<br>26<br>27<br>28<br>29 |

|    | *****                                                                                                                                                              | * INDEX ****** |                                  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------|

|    | <b>§ 7 DMA</b><br>MEMORY TO VRAM<br>VRAM FILL<br>VRAM COPY<br>DMA ABILITY                                                                                          |                | 30<br>30<br>32<br>36<br>38       |

|    | § 8 SCROLL 39<br>SCREEN SIZE<br>HORIZONTAL SCROLL<br>YERTICAL SCROLL<br>SCROLL PATTERN<br>PATTERN NAME                                                             |                | 40<br>41<br>43<br>45<br>46       |

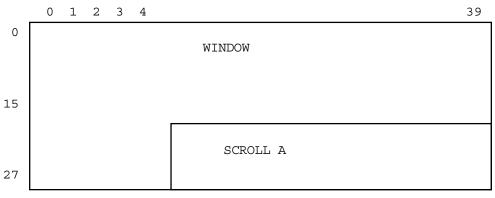

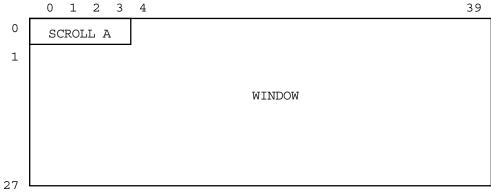

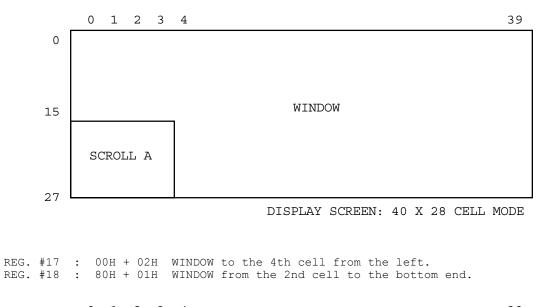

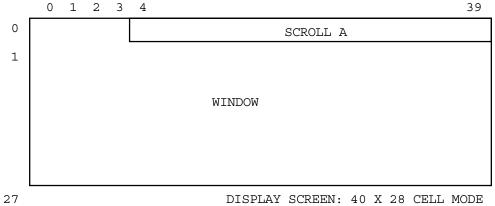

|    | § 9 WINDOW 48<br>POSITION<br>PRIORITY<br>PATTERN NAME                                                                                                              |                | 49<br>52<br>52                   |

|    | <pre>\$ 10 SPRIT_E 54         POSITION         ATTRIBUTE         SIZE         ABILITY         PRIORITY (SPRITES)         PATTERN GENERATER \$ 11 PRIORITY 61</pre> |                | 54<br>56<br>57<br>57<br>58<br>60 |

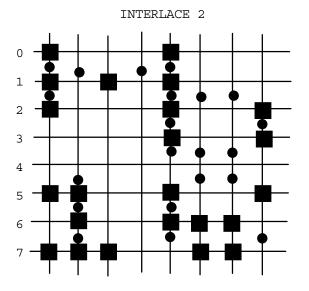

|    | <ul><li>§ 12 COLOR PALETTE 67</li><li>§ 13 INTERLACE MODE 69</li></ul>                                                                                             |                |                                  |

| 3. | 8/16 BIT COMPATIBILITY<br>_ MARK III (MS - JAPAN)<br>_ MS _ RAM CARD                                                                                               |                | 71<br>71<br>71<br>71             |

| 4. | I/O<br>§ 1 VERSION NO. 72                                                                                                                                          |                | 72                               |

|    | <b>§ 2 I/O</b><br><b>§ 3 MEMORY MODE</b> 76                                                                                                                        |                | 72                               |

|    | <b>§ 4 Z80 CONTROLS</b> 76<br>_ Z80 BUSREQ<br>_ Z80 RESET                                                                                                          |                | 76<br>76                         |

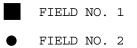

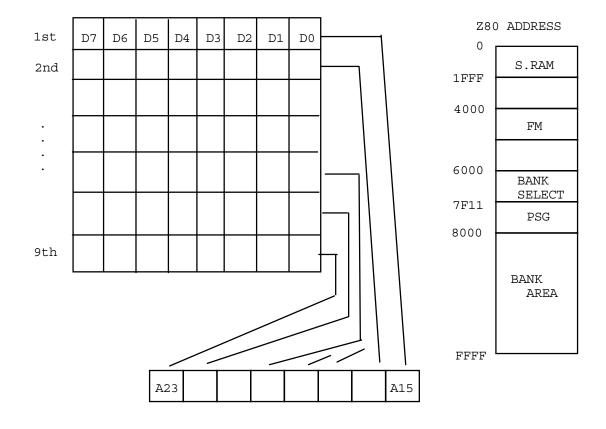

|    | § 5 Z80 AREA<br>_ SOUND RAM<br>_ SOUND CHIP<br>_ BANK REGISTER                                                                                                     |                | 77<br>77<br>77<br>77<br>77       |

|    | VRAM MAPPING<br>APPEND                                                                                                                                             |                | 79<br>XX                         |

Page 6

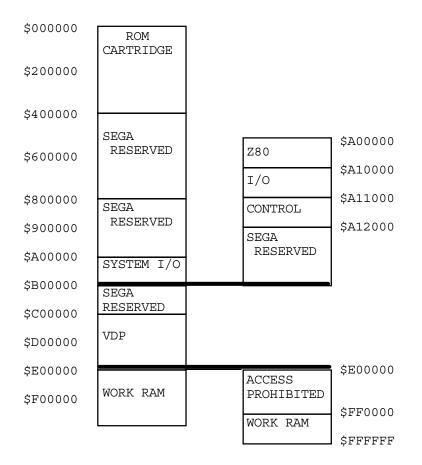

# 1. MEMORY MAP

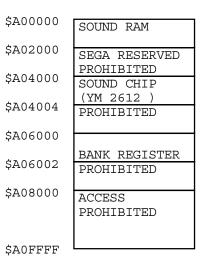

- \$ 1 MEGA DRIVE 16 BIT MODE (AS DISTINCT FROM MASTER SYSTEM COMPATIBILITY MODE)

- \_ 68K MEMORY MAP \_

|         |                          | YM2612             | A0    | 04000 H  |

|---------|--------------------------|--------------------|-------|----------|

| 0000 H  |                          |                    | D0    | 04001 H  |

|         | SOUND RAM                |                    | A1    | 04002 H  |

| 2000 H  | SEGA                     |                    | AT    | 04003 H  |

|         | RESERVED                 |                    | D1    | 04004 11 |

| 4000 H  | SOUND CHIP<br>( YM2612 ) | ACCESS<br>PROHIBIT |       | 04004 H  |

| 6000 H  | MISC.                    | BANK REGI          | ISTER | 06000 H  |

| 0000 11 |                          | ACCESS             | 3     | 06001 H  |

| 8000 H  | 68000 BANK               | PROHIBIT           |       |          |

|         |                          | PSG 7648           | 39    | 07F11 H  |

|         |                          | ACCESS             |       | 07F12 H  |

$\_$  68000 ACCESS TO Z80 MEMORY  $\_$

\_ I/O AREA \_

| \$ A10000              |                      | · · · · · · · · · · · · · · · · · · ·        |  |  |  |  |

|------------------------|----------------------|----------------------------------------------|--|--|--|--|

|                        |                      | Version No.                                  |  |  |  |  |

| \$ A10002<br>\$ A10008 |                      | DATA (CTRL 1)<br>DATA (CTRL 2)<br>DATA (EXP) |  |  |  |  |

|                        |                      | CONTROL (1)<br>CONTROL (2)<br>CONTROL (E)    |  |  |  |  |

| \$ A1000E              |                      | TxDATA<br>RxDATA (1)<br>S-MODE               |  |  |  |  |

| \$ A10014              |                      | TxDATA<br>RxDATA (2)<br>S-MODE               |  |  |  |  |

| \$ A1001A              |                      | TxDATA<br>RxDATA (3)<br>S-MODE               |  |  |  |  |

| \$ A10020              | ACCESS<br>PROHIBITED |                                              |  |  |  |  |

| \$ A1FFFF              |                      |                                              |  |  |  |  |

\_ CONTROL AREA \_

| \$ A11000 | 1                    |

|-----------|----------------------|

|           | MEMORY MODE          |

| \$ A11002 | ACCESS<br>PROHIBITED |

| \$ A11100 | FROMEDIED            |

| Ŷ AIIIO   | Z80 BUSREQ           |

| \$ A11102 | ACCESS<br>PROHIBITED |

| \$ A11200 | Z80 RESET            |

| \$ A11202 | ACCESS<br>PROHIBITED |

| \$ A1FFFF |                      |

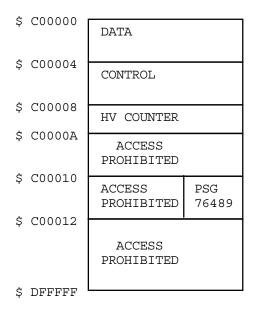

\_ VDP AREA \_

(Video Display Processor)

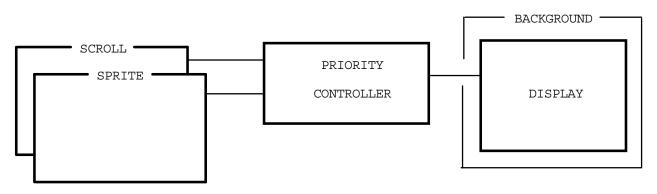

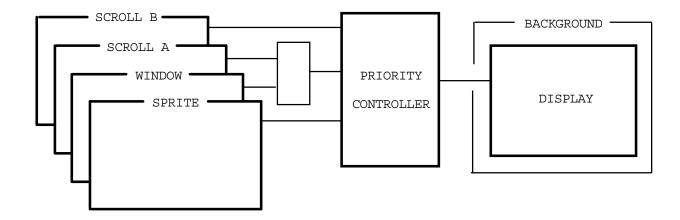

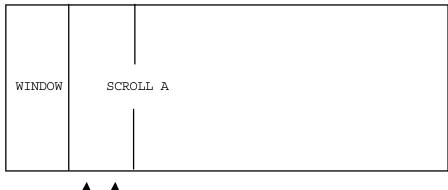

The VDP controls screen display. VDP has graphic modes IV and V. Where Mode IV is for compatibility with the MASTER SYSTEM and V is for the new Mega drive functions. There are no advantages to using mode IV. so it is assumed that all Mega drive development will use mode V. In Mode V. the VDP display has 4 planes: SPRITE, SCROLL A/WINDOW, SCROLL B, and BACKGROUND.

#### GRAPHIC IV MODE (COMPATIBILITY MODE)

GRAPHIC V MODE (16 BIT MODE)

\_ TERMINOLOGY \_

- A unit of Position on X Y coordinates is called a "DOT".

A minimum unit of display is called a "PIXEL".

- "CELL" means an 8 (pixel) x 8 (pixel) pattern.

SCROLL indicated a repositionable screen-spanning play field.

- 5. CPU usually indicates the 68000.

- VDP stands for Video Display Processor.

CTRL stands for Control.

VRAM stands for VDP RAM, the 64K bytes area of RAM accessible only through the VDP.

- 9. CRAM stands for Color RAM, 64 9 bit words inside the VDP chip.

- 10. VSRAM stands for vertical Scroll RAM. 40 10bit words inside the VDP chip.

- DMA stands for Direct Memory Access, the process by which the VDP performs high speed fills or memory copies.

- 12. PSG stands for Programmable sound Generator. A class of low-capability Sound chips. The Mega drive contains a Texas Instruments 76489 PSG chip.

- FM stands for Frequency Modulation, a class of high-capability sound chip. The Mega drive contains a Yamaha 2612 FM chip.

# § 1 DISPLAY SPECIFICATION

## DISPLAY SPECIFICATION OUTLINE

| DISPLAY<br>SIZE      | THERE ARE TWO MODES:<br>32*28 CELL (256*224 PIXEL)<br>40*28 CELL (320*224 PIXEL)                                                                                                                                                                                                                                                        |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHARACTER GENERATOR  | 8*8 CELLS 1300-1800 depending on general system configuration.                                                                                                                                                                                                                                                                          |

| SCROLL<br>PLAYFIELDS | Two scrolling play fields. whose size in cells<br>is selectable from;<br>32*32, 32*64, 32*128,<br>64*32, 64*64, 128*32                                                                                                                                                                                                                  |

| SPRITE               | Sprite size is programmable on a sprite by<br>sprite basis. with the following choices.<br>8*8, 8*16, 8*24, 8*32<br>16*8, 16*16, 16*24, 16*32<br>24*8, 24*16, 24*24, 24*32<br>32*8, 32*16, 32*24, 32*32<br>There are 64 sprites available when the screen<br>is in 32 cell wide mode. Or 80 when the screen<br>is in 40 cell wide mode. |

| WINDOW               | 1 window associated with the Scroll A play field.                                                                                                                                                                                                                                                                                       |

| COLORS               | 64 colors/512 possibilities                                                                                                                                                                                                                                                                                                             |

For PAL (the European Television 50HZ standard), a vertical size of 30 cells (240 dots) is selectable.

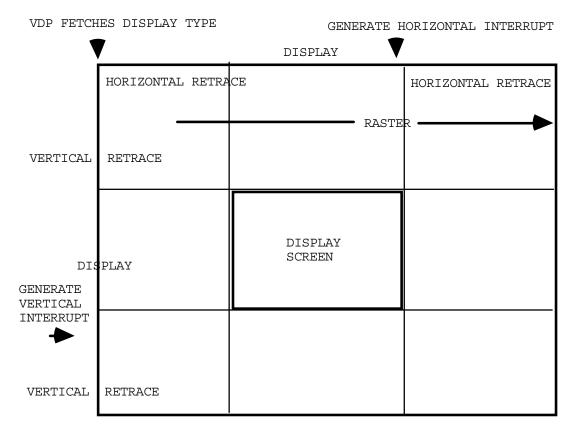

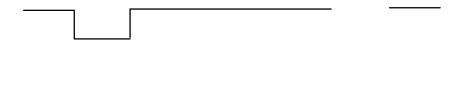

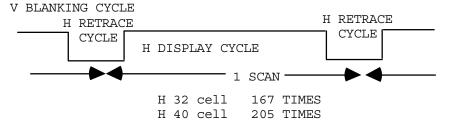

The VDP supports both NTSC and PAL television standards. In both cases, the screen is divided into active scan, where the picture is displayed, and vertical retrace (or vertical blanking) where the monitor prepares for the next display.

Numbers of rasters in a screen are as follows:

|      | Lines/Screen | VCELL | LINE NO.<br>(DISPLAY) | LINE NO.<br>(RETRACE) |

|------|--------------|-------|-----------------------|-----------------------|

| NTSC | 262 28       |       | 224 RASTER            | 38 RASTER             |

| PAL  | 312 28       |       | 224 RASTER            | 98 RASTER             |

| PAL  | 312 30       |       | 240 RASTER            | 82 RASTER             |

#### §2 VDP STRUCTURE

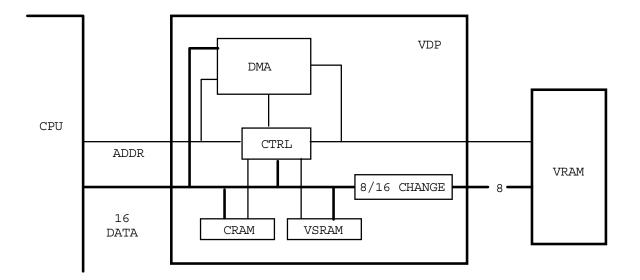

The CPU controls the VDP by special I/O memory locations.

# \_ CTRL (Control)

This controls REGISTER, VRAM, CRAM, VSRAM, DMA DISPLAY, etc.

#### \_ VRAM (VDP RAM) \_

General purpose storage area for display data.

## \_ CRAM (COLOR RAM) \_

64 colors divided into 4 palettes of 16 colors each.

#### \_ VSRAM (Vertical scroll RAM) \_

Up to 20 different vertical scroll values each for scrolling play fields A and B.  $\,$

#### \_ DMA (Direct Memory Access) \_

The VDP may move data at high speed from CPU memory to VRAM, CRAM, and VSRAM instead of the CPU, by taking the 68000 off the bus and doing DMA itself.

The VDP can also fill the VRAM with a constant, or copy from VRAM to VRAM without disturbing the  $68000\,.$

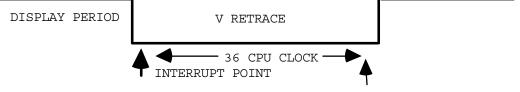

### § 3 INTERRUPT

There are three interrupts: Vertical, Horizontal, and External. You can control each interrupt by the LEO, IE1, and IE2 bits in the VDP registers. The interrupts use the AUTO-VECTOR mode of the 68000 and are at levels 6, 4, and 2 respectively. The level 6 vertical interrupt having the highest priority.

| IE1 H<br>IE2 Ex<br>1                                                                         | Interru<br>Interru<br>ternal Int<br>: Enable<br>: Disable | errupt         | (LEVEL6)<br>(LEVEL4)<br>(LEVEL2) |   |  |  |  |

|----------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------|----------------------------------|---|--|--|--|

| _ <b>VERTICAL INTERRUPT (V-INT)</b> _<br>The vertical interrupt occurs just after V retrace. |                                                           |                |                                  |   |  |  |  |

| DISPLAY                                                                                      | PERIOD                                                    |                |                                  |   |  |  |  |

|                                                                                              |                                                           | INTERRUPT POIN | 1 <b>.</b> Т.                    | — |  |  |  |

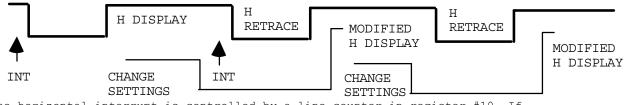

| _ HORIZONTAL INTERRUPT (H-INT) _<br>The horizontal interrupt occurs just before H retrace.   |                                                           |                |                                  |   |  |  |  |

| ים עג.זספדת                                                                                  | FRIOD                                                     |                | F                                |   |  |  |  |

VDP FETCHES INFORMATION FOR THY LINE

The VDP loads the required display information, including all required register values, for the line in about 36 clocks, thus the CPU can control the display of the next line but not the line on which the interrupt occurs.

H SYNC.

The horizontal interrupt is controlled by a line counter in register #10. If this line counter is changed at each interrupt, the desired spacing of interrupts may be achieved.

Thus: If Register #10 equals 00h then the interrupt occurs every line. If Register #10 equals 01h then the interrupt occurs every other line. If Register #10 equals 02h then the interrupt occurs every third line.

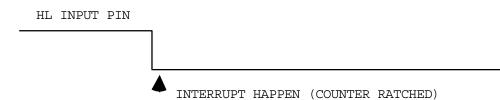

# \_ EXTERNAL INTERRUPT (EX-INT) \_

The external interrupt is generated by a peripheral device (gun, modem) and stops the counter for later examination by the CPU.

Please see other sections of this manual for information about the H, V counter and the initialization of the external interrupt.

# § 4 VDP PORT

The VDP ports are at location 68000 in the 68000 memory space.

| \$ C00000 | DATA PORT      |  |  |  |  |  |

|-----------|----------------|--|--|--|--|--|

| \$ C00002 | "              |  |  |  |  |  |

| \$ C00004 | CONTROL PORT   |  |  |  |  |  |

| \$ C00006 | "              |  |  |  |  |  |

| \$ C00008 | HV COUNTER     |  |  |  |  |  |

| \$ C0000A | PROHIBITED     |  |  |  |  |  |

| \$ C0000C | PROHIBITED     |  |  |  |  |  |

| \$ C0000E | PROHIBITED     |  |  |  |  |  |

| \$ C00010 | PROHIBITED PSG |  |  |  |  |  |

|           |                |  |  |  |  |  |

UPPER BYTE | LOWER BYTE

\_ \$ C00000 (DATA PORT) \_

# READ/WRITE: VRAM, VSRAM, CRAM

| \$ C00000 | DT15  | DT14 | DT13 | DT12 | DT11 | DT10 | DT9 | DT8 | ( D15 | ~ D8 ) |

|-----------|-------|------|------|------|------|------|-----|-----|-------|--------|

| Ş C00000  | DT7   | DT6  | DT5  | DT4  | DT3  | DT2  | DT1 | DT0 | ( D7  | ~ D0 ) |

|           | + 400 | 2000 |      |      | 2    |      |     |     | -     |        |

\* \$C00000 and \$C00002 are functionally equivalent.

# \_ \$ C00004 (CONTROL PORT) \_

| READ :                                                                                                           | STATUS | REGIS            | TER    |                 |       |       |              |          |              |

|------------------------------------------------------------------------------------------------------------------|--------|------------------|--------|-----------------|-------|-------|--------------|----------|--------------|

| \$ C00004                                                                                                        | *      | *                | *      | *               | *     | *     | EMPT         | FULL     | ( D15 ~ D8 ) |

| \$ 00004                                                                                                         | F      | SOVR             | С      | ODD             | DT3   | VB    | HB           | B PAL    | ( D7 ~ D0 )  |

| * NO USE                                                                                                         |        |                  |        |                 |       |       |              |          |              |

| EM                                                                                                               |        | l: WRI           | TE FII | FO EMP          | ΥΤΥ   |       |              |          |              |

| FU                                                                                                               |        | l: WRI           | TE FI  | FO FUL          | ιL    |       |              |          |              |

| F                                                                                                                | 1      | l: V i           | nterru | upt ha          | ppene | ed.   |              |          |              |

| SOVR 1: Sprites overflow occurred, too many in one line.<br>Over 17 in 32 cell mode.<br>Over 21 in 40 cell mode. |        |                  |        |                 |       |       | in one line. |          |              |

| С                                                                                                                |        |                  |        | n happ<br>sprit |       | betwe | en nor       | n-zero p | pixels       |

| ODI                                                                                                              |        | l: Odd<br>): Eve |        |                 |       |       |              |          |              |

| VB                                                                                                               |        | l: Dur           | ing V  | blank           | ing   |       |              |          |              |

| HB                                                                                                               |        | l: Dur           | ing H  | blank           | ing   |       |              |          |              |

| DM                                                                                                               |        | l: DMA<br>):     | BUSY   |                 |       |       |              |          |              |

| PA                                                                                                               |        | l: PAL<br>): NTS |        | Ξ               |       |       |              |          |              |

# WRITE1 : REGISTER SET

WRITE2 : ADDRESS SET

| \$ C00004 |   | 1     | 0    | 0      | RS4   | RS3   | RS2  | RS1    | RS0    | ( D15 ~ D8 ) |

|-----------|---|-------|------|--------|-------|-------|------|--------|--------|--------------|

| Ş C00004  |   | D7    | D6   | D5     | D4    | D3    | D2   | D1     | DO     | ( D7 ~ D0 )  |

|           | * | \$C00 | 0004 | and \$ | C0000 | 6 are | func | ctiona | illy e | quivalent.   |

RS4 ~ RS0 : Register No. D7 ~ D0 : Date

$\star$  You must use word or long word access to VDP ports when setting the registers. Long word access is equivalent to two word accesses, with D31-D16 written first.

| 1st<br>\$ C00004 | CD1<br>A7  | CD0<br>A6               | A13<br>A5 | A12<br>A4 | A11<br>A3 | A10<br>A2 | A9<br>A1 | A8<br>A9 | ( D15<br>( D7 | ~ D8 )<br>~ D0 ) |

|------------------|------------|-------------------------|-----------|-----------|-----------|-----------|----------|----------|---------------|------------------|

| 2nd              | 0          | 0                       | 0         | 0         | 0         | 0         | 0        | 0        |               | ~ D8 )           |

| \$ C00004        | CD5<br>CD3 | CD4<br>5 ~ CD<br>5 ~ A0 |           | ID C      | ODE       |           | A1       |          | ( D7          | ~ D0 )           |

| ACCE             | SS MODE    |                         | •         | DESI      | CD5 (     | DN RAM    | CD       |          | CD1 d         | DO               |

|                  | WRITE      |                         |           |           | 0 0       |           | 0        |          | 0 1           | DU               |

| CRAM             | WRITE      |                         |           |           | 0 0       |           | 0        | 0        | 1 1           |                  |

| VSRA             | M WRITE    |                         |           |           | 0 0       |           | 0        | 1        | 0 1           |                  |

| VRAM             | READ       |                         |           |           | 0 0       |           | 0        | 0        | 0 0           |                  |

| CRAM             | READ       |                         |           |           | 0 0       |           | 1        | 0        | 0 0           |                  |

| VSRA             | M READ     |                         |           |           | 0 0       |           | 0        | 1        | 0 0           |                  |

\* You must use word or long word when performing these operations.

Page 20

\_ \$ C00008 (HV Counter) \_

# NON INTERLACE MODE

| \$ C00008 | VC7 | VC6  | VC5  | VC4   | VC3   | VC2  | VC1   | VC0   |   | ( D15 | ~ | D8 | ) |

|-----------|-----|------|------|-------|-------|------|-------|-------|---|-------|---|----|---|

| \$ 00000  | HC  | 8 HC | 7 HC | 5 HC! | 5 HC4 | 4 HC | B HC2 | 2 HC1 | ] | ( D7  | ~ | D0 | ) |

# INTERLACE MODE

| \$ C00008 | VC7 | VC6            | VC5 | VC4   | VC3   | VC2  | VC1  | VC8   | (   | D15 | ~ | D8 | ) |

|-----------|-----|----------------|-----|-------|-------|------|------|-------|-----|-----|---|----|---|

| Ş C00008  | HC  | B HC7          | HCe | 5 HCS | 5 HC4 | 4 HC | 3 HC | 2 HC1 | ) ( | D7  | ~ | D0 | ) |

|           |     | HC8 ~<br>VC8 ~ |     |       |       |      |      |       | _   |     |   |    |   |

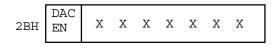

#### § 4 VDP REGISTER

VDP has write only register #0 through #23 and read only status register total 25 register. These are two modes for register settings. One is mode 4 and another is mode 5. We tell you about mode 5 in this section and about mode 4 see MARK section. If you change mode in one frame you can get various effects.

# MODE SET REGISTER No. 1

|          | MSB       |          |                |                                        |                  |      |    | LSB |

|----------|-----------|----------|----------------|----------------------------------------|------------------|------|----|-----|

| REG. # 0 | 0         | 0        | 0              | IE1                                    | 0                | 1    | МЗ | 0   |

|          | IE1<br>M3 | 0:<br>1: | Disab<br>HV. C | e H int<br>le H in<br>ounter<br>e read | iterrupi<br>stop | (REG |    | 4)  |

#### MODE SET REGISTER No. 2

|          | MSB |         |                  |    |                      |        |         | LSB    |       |

|----------|-----|---------|------------------|----|----------------------|--------|---------|--------|-------|

| REG. # 1 | 0   | DISP    | IE0              | M1 | M2                   | 1      | 0       | 0      |       |

| DI       |     | : Enak  |                  |    |                      |        |         | -      | -     |

| IE       |     | : Enak  |                  |    | upt (6800<br>Supt    | 0 Leve | 16)     |        |       |

| M1       |     | DMA DMA | Enable<br>Disabl |    |                      |        |         |        |       |

| M2       |     |         |                  |    | PAL mode<br>Pal mode |        | ys 0 ir | NTSC 1 | mode) |

#### PATTERN NAME TABLE BASE ADDRESS FOR SCROLL A

#### PATTERN NAME TABLE BASE ADDRESS FOR WINDOW

|          | MSB                |          |         |         |         |       |         | LSB |

|----------|--------------------|----------|---------|---------|---------|-------|---------|-----|

| REG. # 3 | 0                  | 0        | WD15    | WD14    | WD13    | WD12  | WD11    | 0   |

|          | WD11 sh<br>VRAM AD | DR \$ XX | xxx_x00 | 0_0000_ | 0000 (H |       |         | ,   |

|          | VRAM AD            | DR \$ XX | XXX_000 | 0_0000_ | 0000 (H | 40 ce | ll mode | e ) |

# PATTERN NAME TABLE BASE ADDRESS FOR SCROLL B

|          | MSB    |          |         |         |      |      |      | LSB  |

|----------|--------|----------|---------|---------|------|------|------|------|

| REG. # 4 | 0      | 0        | 0       | 0       | 0    | SB15 | SB14 | SB13 |

|          | VRAM A | DDR \$XX | XXO_000 | 0_0000_ | 0000 |      |      |      |

# SPRITE ATTRIBUTE TABLE BASE ADDRESS

|        |        | MSB     |                                                                                                                       |      |      |      | -    |      | LSB |  |  |

|--------|--------|---------|-----------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|-----|--|--|

| REG.   | # 5    | 0       | AT15                                                                                                                  | AT14 | AT13 | AT12 | AT11 | AT10 | AT9 |  |  |

|        |        | VRAM AD | should be 0 in H 40 cell mode<br>4 ADDR \$XXXX_XXX0_0000_0000 ( 32 cell )<br>4 ADDR \$XXXX_XX00_0000_0000 ( 40 cell ) |      |      |      |      |      |     |  |  |

|        |        | MSB     |                                                                                                                       |      |      |      |      |      | LSB |  |  |

| REG.   | # 6    | 0       | 0                                                                                                                     | 0    | 0    | 0    | 0    | 0    | 0   |  |  |

| BACKGR | OUND C | OLOR    |                                                                                                                       |      |      |      |      |      |     |  |  |

|          | MSB              |                  |      |      |      |      |      | LSB  |

|----------|------------------|------------------|------|------|------|------|------|------|

| REG. # 7 | 0                | 0                | CPT1 | CPT0 | COL3 | COL2 | COL1 | COL0 |

|          | CPT1,0<br>COL3 ~ | : COI<br>0 : COI |      |      |      |      |      |      |

|          | MSB              |                  |      |      |      |      |      | LSB  |

| REG. # 8 | 0                | 0                | 0    | 0    | 0    | 0    | 0    | 0    |

|          | MSB              |                  |      |      |      |      |      | LSB  |

| REG. # 9 | 0                | 0                | 0    | 0    | 0    | 0    | 0    | 0    |

H INTERRUPT REGISTER

|          | MSB  |      |      |      |      |      |      | LSB  |

|----------|------|------|------|------|------|------|------|------|

| REG. #10 | BIT7 | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 | BIT0 |

This register makes H interrupt timing by number of Raster H interrupt is enabled by  $\mbox{IE=1}$

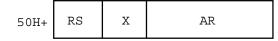

# MODE SET REGISTER No. 3

\* BOTH SCROLL A AND B

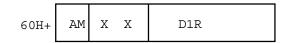

# MODE SET REGISTER No. 4

|          | MSB     |         |         |         |          |         |      | LSB |

|----------|---------|---------|---------|---------|----------|---------|------|-----|

| REG. #12 | RS0     | 0       | 0       | 0       | S/TE     | LSM1    | LSM0 | RS1 |

|          | RS0     | 0: Hoi  | rizonta | 1 32 ce | ell mode | e       |      |     |

|          |         | 1: Hoi  | rizonta | 1 40 ce | ell mode | Э       |      |     |

|          | RS1     | 0: Hoi  | rizonta | 1 32 ce | ell mode | e       |      |     |

|          |         | 1: Hoi  | rizonta | 1 40 ce | ell mode | e       |      |     |

|          | * Yo    | u shoul | ld set  | same No | o. in RS | SO, RS1 |      |     |

|          |         | 32 cel: | l 0000  | XXX0    |          |         |      |     |

|          |         | 40 cel: | l 1000  | XXX1    |          |         |      |     |

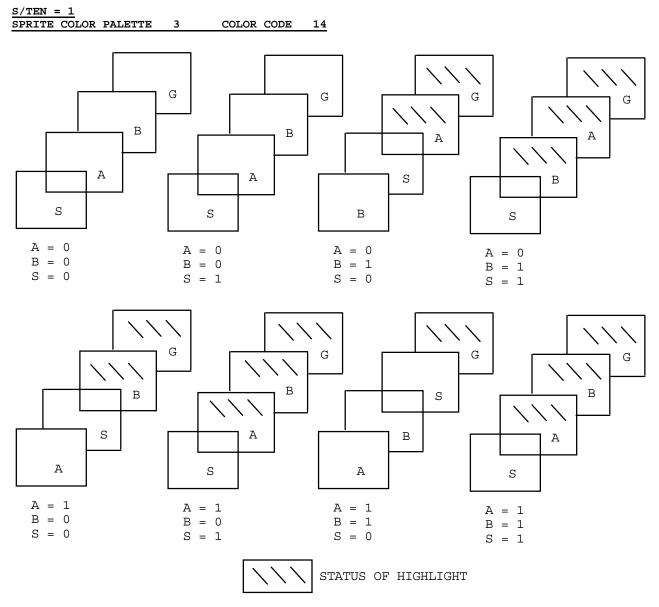

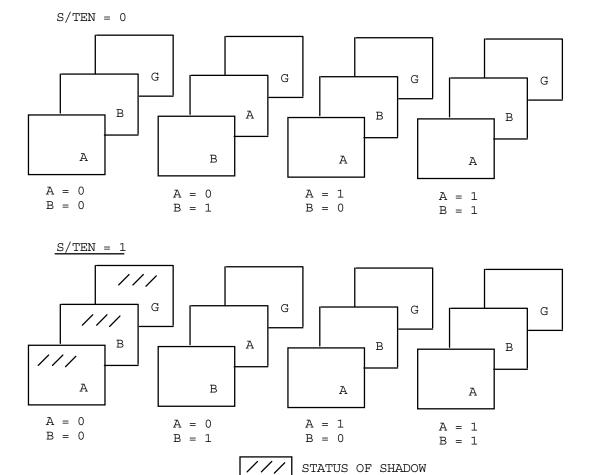

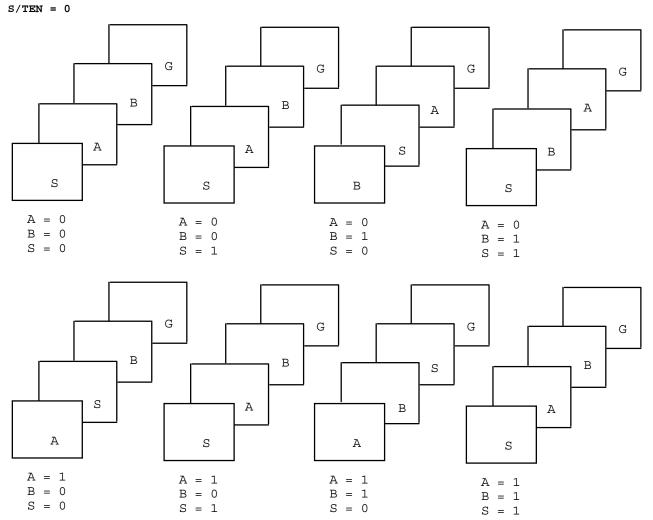

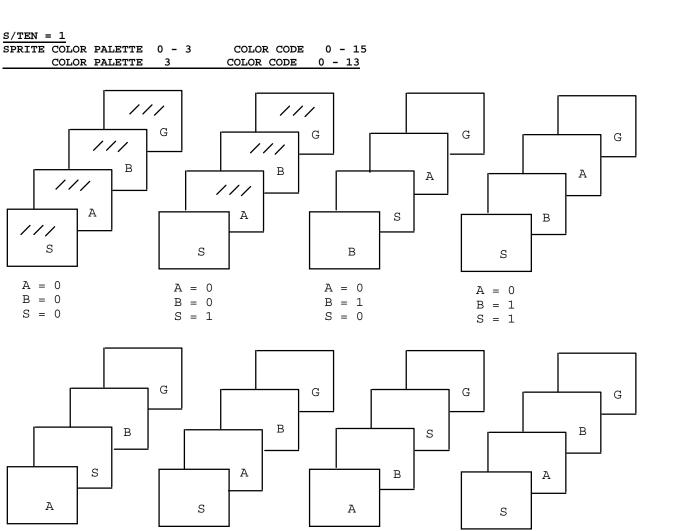

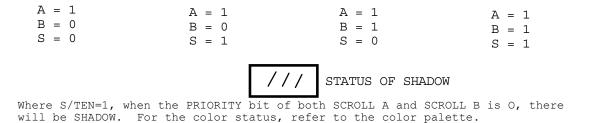

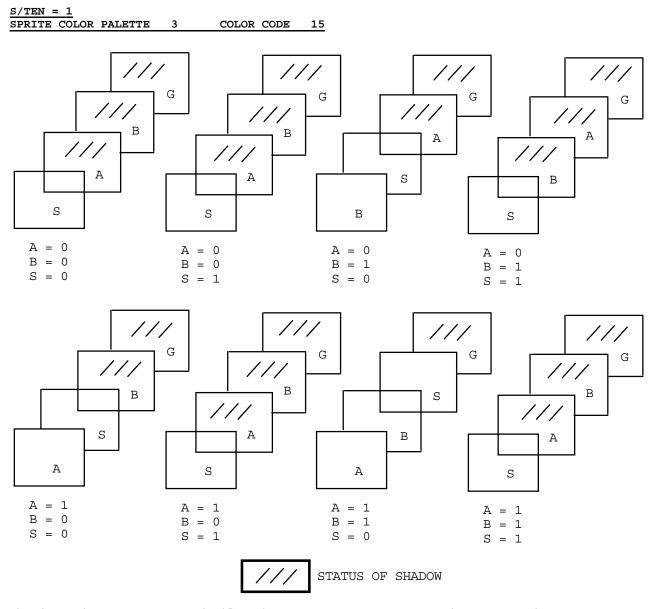

|          | S/TE    | 1: Ena  | able SH | ADOW an | d HIGH   | LIGHT.  |      |     |

|          |         | 0: Dis  | sable S | HADOW a | and HIG  | HLIGHT. |      |     |

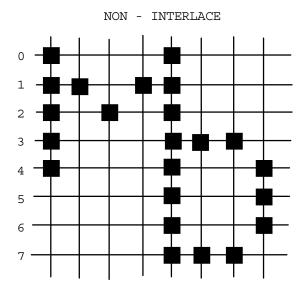

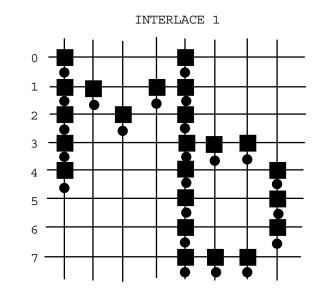

|          | LSM1, I | SMO: In | nterlac | e mode  | setting  | g       |      |     |

|          |         |         |         |         |          |         |      |     |

|          | LSM1    | LS MO   |         | FU      | JNCTION  |         |      |     |

|          | 0 0     |         |         | NO      | INTERLA  | CE      |      |     |

INTERLACE

PROHIBITED

INTERLACE (Double Resolution)

H SCROLL DATA TABLE BASE ADDRESS

0

1

1

1

1

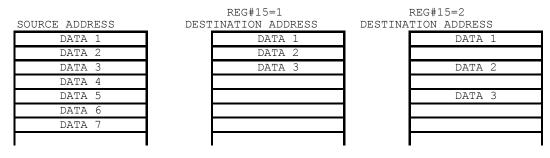

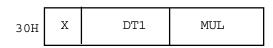

AUTO INCREMENT DATA This register controls bias number of increment data.

|          | MSB    | _       |         |         |        |      |      | LSB  |

|----------|--------|---------|---------|---------|--------|------|------|------|

| REG. #15 | INC7   | INC6    | INC5    | INC4    | INC3   | INC2 | INC1 | INC0 |

|          | INC7 ~ | 0: Bias | s numbe | r ( 0 ~ | \$FF ) |      | -    |      |

This number is added automatically after ram access.

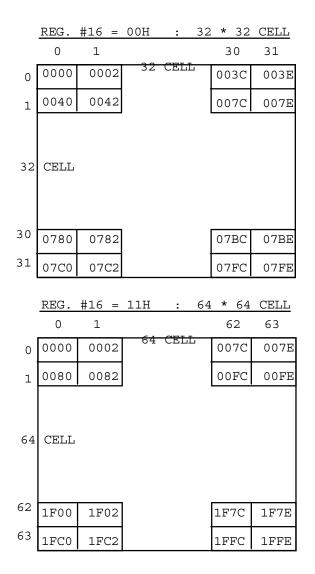

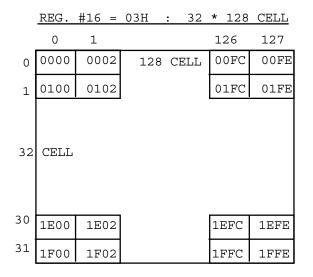

# SCROLL SIZE

|      |     | MSB |   |      |      |   | - |      | LSB  |

|------|-----|-----|---|------|------|---|---|------|------|

| REG. | #16 | 0   | 0 | VSZ1 | VSZ0 | 0 | 0 | HSZ1 | HSZ0 |

| VSZ0 | SZO FUNCTION |  |  |  |  |  |  |  |

|------|--------------|--|--|--|--|--|--|--|

|      | V 32 cell    |  |  |  |  |  |  |  |

|      | V 64 cell    |  |  |  |  |  |  |  |

|      | PROHIBITED   |  |  |  |  |  |  |  |

| 1    | V 128 cell   |  |  |  |  |  |  |  |

|      | <b>vsz0</b>  |  |  |  |  |  |  |  |

| HSZ1 | HSZ0 | FUNCTION   |

|------|------|------------|

| 0 0  |      | H 32 cell  |

| 0 1  |      | H 64 cell  |

| 1 0  |      | PROHIBITED |

| 1    | 1    | H 128 cell |

\* Both of scroll A and B

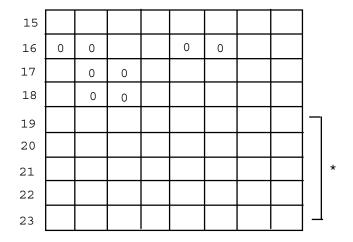

# WINDOW H POSITION

|          | MSB            |         |         |                  |         |               |                    |      |  |  |

|----------|----------------|---------|---------|------------------|---------|---------------|--------------------|------|--|--|

| REG. #17 | RIGT           | IGT 0 0 |         | WHP5             | WHP4    | WHP3          | WHP2               | WHP1 |  |  |

|          | RIGT<br>WHP5 ~ | 1: Wir  | ndow is | in rig<br>ter 0= | nt side | e from<br>ide | ase poi<br>base po |      |  |  |

# WINDOW V POSITION

|          | MSB    |                                                                                    |                                               |      |      |      |      | LSB  |  |  |  |  |

|----------|--------|------------------------------------------------------------------------------------|-----------------------------------------------|------|------|------|------|------|--|--|--|--|

| REG. #18 | DOWN   | 0                                                                                  | 0                                             | WVP4 | WVP3 | WVP2 | WVP1 | WVP0 |  |  |  |  |

|          | DOWN   | 0 : Window is in upper side from base p<br>1 : Window is in lower side from base p |                                               |      |      |      |      |      |  |  |  |  |

|          | WVP4 ~ | 0 Ва                                                                               | 0 Base pointer 0=Upper side<br>1= 1 cell down |      |      |      |      |      |  |  |  |  |

|          |        |                                                                                    |                                               | 2    |      |      |      |      |  |  |  |  |

| MSB      |     |     |     |     |     |     |     |     |  |

|----------|-----|-----|-----|-----|-----|-----|-----|-----|--|

| REG. #19 | LG7 | LG6 | LG5 | LG4 | LG3 | LG2 | LG1 | LG0 |  |

# DMA LENGTH COUNTER HIGH

|                              | MSB  |      |      |      |      |      |     | LSB |  |  |  |

|------------------------------|------|------|------|------|------|------|-----|-----|--|--|--|

| REG. #20                     | LG15 | LG14 | LG13 | LG12 | LG11 | LG10 | LG9 | LG8 |  |  |  |

| LG15 ~ 0: DMA LENGTH COUNTER |      |      |      |      |      |      |     |     |  |  |  |

DMA SOURCE ADDRESS LOW

# DMA SOURCE ADDRESS MID

| MSB      |      |      |      |      |      |      |      |     |  |  |

|----------|------|------|------|------|------|------|------|-----|--|--|

| REG. #22 | SA16 | SA15 | SA14 | SA13 | SA12 | SA11 | SA10 | SA9 |  |  |

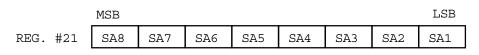

DMA SOURCE ADDRESS HIGH

|                                                     | MSB  |      |      |      |      |      |      |      |  |  |  |  |

|-----------------------------------------------------|------|------|------|------|------|------|------|------|--|--|--|--|

| REG. #23                                            | DMD1 | DMD0 | SA22 | SA21 | SA20 | SA19 | SA18 | SA17 |  |  |  |  |

| SA22 ~ 1 : DMA Source address<br>DMD1, 0 : DMA MODE |      |      |      |      |      |      |      |      |  |  |  |  |

| 0 | : | DMA | MODE |  |

|---|---|-----|------|--|

|   |   |     |      |  |

| DMD1 | DMD0 | FUNCTION       |

|------|------|----------------|

| 0 S  | A23  | MEMORY TO VRAM |

| 1 0  |      | VRAM FILL      |

| 1 1  |      | VRAM COPY      |

# § 6 ACCESS VDP RAM

# \_ RAM ADDRESS SETTING \_

You can access VRAM CRAM and VSRAM after writing 32 bits of control data to C000004 or C000006.

You have to use word or long word when addressing. If you use long word D31 - D16 is 1st, D15 - D0 2nd.

| 1st       | CD1 |     | CD0 | A13   | A12   | A11  | A10 | I | <del>1</del> 9 | A8  | ( D15 | ~ D8 ) |

|-----------|-----|-----|-----|-------|-------|------|-----|---|----------------|-----|-------|--------|

| \$ C00004 | I   | 17  | A6  | A5    | A4    | A3   | A2  | 2 | A1             | A9  | (D7   | ~ D0 ) |

|           |     |     |     |       |       |      |     |   |                |     |       |        |

| 2nd       | 0   |     | 0   | 0     | 0     | 0    | 0   |   | 0              | 0   | ( D15 | ~ D8 ) |

| \$ C00004 | CI  | )5  | CD4 | 4 CD: | 3 CD. | 2 0  | (   | ) | A15            | A14 | (D7 · | ~ D0 ) |

|           |     | CDS | 5~0 | CDO : | ID (  | CODE |     |   |                |     | _     |        |

A15 ~ A0 : DESTINATION RAM ADDRESS

|             | CD5 | CD4 | CD3 | CD2 | CD1 | CD0 |

|-------------|-----|-----|-----|-----|-----|-----|

| VRAM WRITE  | 0 0 | 0   | 0   | 0   | 1   |     |

| CRAM WRITE  | 0 0 | 0   | 0   | 1   | 1   |     |

| VSRAM WRITE | 0 0 | 0   | 1   | 0   | 1   |     |

| VRAM READ   | 0 0 | 0   | 0   | 0   | 0   |     |

| CRAM READ   | 0 0 | 1   | 0   | 0   | 0   |     |

| VSRAM READ  | 0 0 | 0   | 1   | 0   | 0   |     |

VRAM address range from 0 to 0FFFF H, 64K bytes total. VRAM access addressing is as follow when writing:

| 1st                     | 0   | 1    | A13    | A12  | A11     | A10  | A9  | A8    | ( D15 ~ D8 ) |  |  |  |

|-------------------------|-----|------|--------|------|---------|------|-----|-------|--------------|--|--|--|

| \$ C00004               | A7  | A    | 6 A    | 5 A4 | A3      | A2   | A1  | L AO  | ( D7 ~ D0 )  |  |  |  |

|                         |     |      |        |      |         |      |     |       |              |  |  |  |

| 2nd                     | 0   | 0    | 0      | 0    | 0       | 0    | 0   | 0     | ( D15 ~ D8 ) |  |  |  |

| \$ C00004               | C   | 0    | 0      | 0    | 0       | 0    | A15 | 5 A14 | ( D7 ~ D0 )  |  |  |  |

| A15 ~ A0 : VRAM address |     |      |        |      |         |      |     |       |              |  |  |  |

|                         |     |      |        |      |         |      |     |       |              |  |  |  |

| Data                    | D15 | D14  | D13    | D12  | D11     | D10  | D9  | D8    | ( D15 ~ D8 ) |  |  |  |

| \$ C00000               | E   | 7 D6 | D5     | D4   | 1 D3    | 3 D2 | D1  | DO    | ( D7 ~ D0 )  |  |  |  |

|                         |     | D1   | 5 ~ D0 | : V  | 'RAM da | ata  |     |       |              |  |  |  |

When you use long word D31  $\sim$  D16 is 1st. D15  $\sim$  D0 2nd. When you do byte writing, data is D7  $\sim$  D0, and may be written to \$C00000 or \$C00001. VRAM address is increased by the value of REGISTER # 15. independent data size. VRAM address A0 is used in the calculation of the address increment, but is ignored during address decoding.

VRAM addressing and decoding are as follows: the CRAM address decode uses A15  $\sim$  A1, and A0 specifies the data write format. Write data can not cross a word boundary high and low bytes are exchanged if A0=1.

| A0=0                 | BYTE    | WORD                | LONG WORD              |

|----------------------|---------|---------------------|------------------------|

| ADDRESS: EVEN<br>ODD | D7 ~ D0 | D15 ~ D8<br>D7 ~ D0 | D31 ~ D24<br>D23 ~ D16 |

| ADDRESS: EVEN<br>ODD |         |                     | D15 ~ D8<br>D7 ~ D0    |

|                      |         |                     |                        |

|                      |         |                     |                        |

| A0=1                 | BYTE    | WORD                | LONG WORD              |

| ADDRESS: EVEN<br>ODD | D7 ~ D0 | D7 ~ D0<br>D15 ~ D8 | D23 ~ D16<br>D31 ~ D24 |

| ADDRESS: EVEN<br>ODD |         |                     | D7 ~ D0<br>D15 ~ D8    |

| (EXAMPLE)<br>START ADDRESS: 0 | REG. #15=2  |              |               |

|-------------------------------|-------------|--------------|---------------|

|                               | BYTE        | WORD         | LONG WORD     |

| ADDRESS: 0                    | 1st D7 ~ D0 | 1st D15 ~ D8 | 1st D31 ~ D24 |

| 1                             |             | D7 ~ D0      | D23 ~ D16     |

| ADDRESS: 2                    | 2nd D7 ~ D0 | 2nd D15 ~ D8 | 1st D15 ~ D8  |

| 3                             |             | D7 ~ D0      | D7 ~ D0       |

| ADDRESS: 4                    | 3rd D7 ~ D0 | 3rd D15 ~ D8 | 2nd D31 ~ D24 |

| 5                             |             | D7 ~ D0      | D23 ~ D16     |

| ADDRESS: 6                    | 4th D7 ~ D0 | 4th D15 ~ D8 | 2nd D15 ~ D8  |

| 7                             |             | D7 ~ D0      | D7 ~ D0       |

| ADDRESS: 8                    | 5th D7 ~ D0 | 5th D15 ~ D8 | 3rd D31 ~ D24 |

| 9                             |             | D7 ~ D0      | D23 ~ D16     |

|                               |             |              |               |

# START ADDRESS: 0 REG. #15=1

|                 | BYTE                        |  | WORD                     | LONG WORD               |

|-----------------|-----------------------------|--|--------------------------|-------------------------|

| ADDRESS: 0<br>1 | 2nd D7 ~ D0<br>1st D7 ~ D0  |  | 2nd D7 ~ D0<br>D15 ~ D8  | 1st D7 ~ D0<br>D15 ~ D8 |

| ADDRESS: 2<br>3 | 4th D7 ~ D0<br>3rd D7 ~ D0  |  | 4th D7 ~ D0<br>D15 ~ D8  | 2nd D7 ~ D0<br>D15 ~ D8 |

| ADDRESS: 4<br>5 | 6th D7 ~ D0<br>5th D7 ~ D0  |  | 6th D7 ~ D0<br>D15 ~ D8  | 3rd D7 ~ D0<br>D15 ~ D8 |

| ADDRESS: 6<br>7 | 8th D7 ~ D0<br>7th D7 ~ D0  |  | 8th D7 ~ D0<br>D15 ~ D8  | 4th D7 ~ D0<br>D15 ~ D8 |

| ADDRESS: 8<br>9 | 10th D7 ~ D0<br>9th D7 ~ D0 |  | 10th D7 ~ D0<br>D15 ~ D8 | 5th D7 ~ D0<br>D15 ~ D8 |

|            | BYTE        | WORD        | LONG WORD     |

|------------|-------------|-------------|---------------|

| ADDRESS: 0 | 1st D7 ~ D0 | 1st D7 ~ D0 | 1st D23 ~ D16 |

| 1          |             | D15 ~ D8    | D31 ~ D24     |

| ADDRESS: 2 | 2nd D7 ~ D0 | 2nd D7 ~ D0 | 1st D23 ~ D16 |

| 3          |             | D15 ~ D8    | D31 ~ D24     |

| ADDRESS: 4 | 3rd D7 ~ D0 | 3rd D7 ~ D0 | 2nd D23 ~ D16 |

| 5          |             | D15 ~ D8    | D31 ~ D24     |

| ADDRESS: 6 | 4th D7 ~ D0 | 4th D7 ~ D0 | 2nd D23 ~ D16 |

| 7          |             | D15 ~ D8    | D31 ~ D24     |

| ADDRESS: 8 | 5th D7 ~ D0 | 5th D7 ~ D0 | 3rd D23 ~ D16 |

| 9          |             | D15 ~ D8    | D31 ~ D24     |

|            |             | 1           |               |

# START ADDRESS: 1 REG. #15=2

# START ADDRESS: 1 REG. #15=1

|                 | BYTE                       |  | WORD                    |   | LONG WORD                  |

|-----------------|----------------------------|--|-------------------------|---|----------------------------|

| ADDRESS: 0<br>1 | 1st D7 ~ D7                |  | 1st D7 ~ D0<br>D15 ~ D8 |   | 1st D23 ~ D16<br>D31 ~ D24 |

| ADDRESS: 2<br>3 | 3rd D7 ~ D7<br>2nd D7 ~ D7 |  | 3rd D7 ~ D0<br>D15 ~ D8 |   | 2nd D23 ~ D16<br>D31 ~ D24 |

| ADDRESS: 4<br>5 | 5th D7 ~ D7<br>4th D7 ~ D7 |  | 5th D7 ~ D0<br>D15 ~ D8 |   | 3rd D23 ~ D16<br>D31 ~ D24 |

| ADDRESS: 6<br>7 | 7th D7 ~ D7<br>6th D7 ~ D7 |  | 7th D7 ~ D0<br>D15 ~ D8 |   | 4th D23 ~ D16<br>D31 ~ D24 |

| ADDRESS: 8<br>9 | 9th D7 ~ D7<br>8th D7 ~ D7 |  | 9th D7 ~ D0<br>D15 ~ D8 |   | 5th D23 ~ D16<br>D31 ~ D24 |

|                 |                            |  |                         | T |                            |

# VRAM READ

| 1st       | 0                    | 0    | A13   | A12  | A11    | A10    | A9  | A8    | (D15 ~ D8)   |  |  |

|-----------|----------------------|------|-------|------|--------|--------|-----|-------|--------------|--|--|

| \$ C00004 | A7                   | A    | 5 AS  | 5 A4 | A3     | A2     | A   | 1 A0  | ( D7 ~ D0 )  |  |  |

| 2nd       | 0                    | 0    | 0     | 0    | 0      | 0      | 0   | 0     | ( D15 ~ D8 ) |  |  |

| \$ C00004 | 0                    | 0    | 0     | 0    | 0      | 0      | A15 | 5 A14 | ( D7 ~ D0 )  |  |  |

|           |                      | A1   | 5 ~ A | 0:   | VRAM a | addres | S   |       |              |  |  |

| -         |                      |      |       |      |        |        |     |       |              |  |  |

| Data      | D15                  | D14  | D13   | D12  | D11    | D10    | D9  | D8    | ( D15 ~ D8 ) |  |  |

| \$ C00000 | D                    | 7 D6 | D5    | D4   | 1 D3   | 3 D2   | D1  | D0    | ( D7 ~ D0 )  |  |  |

|           | D15 ~ D0 : VRAM data |      |       |      |        |        |     |       |              |  |  |

The data is always read in word units. A0 is ignored during the read; no swap of bytes occurs if A0=1. Subsequent reads are from address incremented by REGISTER #15. A0 is used in calculation of the next address.

# \_ CRAM ACCESS \_

The CRAM contains 128 bytes, addresses 0 to 7FH. For word wide writes to the CRAM, use:

| lst       | 1 | _  | 1  | 0      | 0    | 0    | 0     | 0  | 0  | - | ( D15 ~ D8 ) |

|-----------|---|----|----|--------|------|------|-------|----|----|---|--------------|

| \$ C00004 |   | 0  | A  | 5 A.   | 5 A4 | A3   | A2    | A1 | A0 |   | ( D7 ~ D0 )  |

| r         |   |    |    |        |      |      |       |    |    |   |              |

| 2nd       | C | )  | 0  | 0      | 0    | 0    | 0     | 0  | 0  | _ | ( D15 ~ D8 ) |

| \$ C00004 |   | 0  | 0  | 0      | 0    | 0    | 0     | 0  | 0  |   | ( D7 ~ D0 )  |

|           |   |    |    | A6 ~ . | A0 : | VRAM | addre | SS | -  | _ |              |

| _         |   |    |    |        |      |      |       |    |    |   |              |

| Data      | C | )  | 0  | 0      | 0    | B2   | B1    | B0 | 0  | _ | ( D15 ~ D8 ) |

| \$ C00000 |   | G2 | G1 | G0     | 0    | R2   | R1    | R0 | 0  |   | ( D7 ~ D0 )  |

D15 ~ D0 are valid when we use word for data set. If the writes are byte wide, write the high byte to 00000 and the low byte to 00001. A long word wide access is equivalent to two sequential word wide accesses. Place the first data in D31 - D16 and the second data in D15 - D0. The date may be written sequentially; the address is incremented by the value of REGISTER #15 after every write, independent of whether the width is byte of word.

Note that A0 is used in the increment but not in address decoding, resulting in some interesting side-effects if writes are attempted at odd addresses.

For word wide reads from the CRAM, use:

| lst                    | 0 | 0  | 0<br>A6 | 0<br>5 A | 0<br>5 A4 | 0<br>A3 | 0<br>A2 | 0<br>A: | 0<br>1 A0 | 7 | ( D15 ~ D8 )<br>( D7 ~ D0 ) |

|------------------------|---|----|---------|----------|-----------|---------|---------|---------|-----------|---|-----------------------------|

| \$ C00004              |   | 0  | Ad      | A        | D A4      | AS      | AZ      | A.      |           |   | ( 00 ~ 00 )                 |

| 2nd                    | 0 |    | 0       | 0        | 0         | 0       | 0       | 0       | 0         | _ | ( D15 ~ D8 )                |

| \$ C00004              |   | 0  | 0       | 1        | 0         | 0       | 0       | 0       | 0         |   | ( D7 ~ D0 )                 |

| A6 ~ A0 : VRAM address |   |    |         |          |           |         |         |         |           |   |                             |

| Data                   | * |    | *       | *        | *         | B2      | B1      | B0      | *         | _ | ( D15 ~ D8 )                |

| \$ C00000              | ( | G2 | G1      | G0       | *         | R2      | R1      | RO      | *         |   | ( D7 ~ D0 )                 |

#### \_ VSRAM ACCESS \_

The VSRAM contains 80 bytes, addresses 0 to 4FH. For word wide writes to the VSRAM, use:

| 1st                     | 0  | 1      | 0     | 0     | 0     | 0      | 0 0       | (D15 ~ D8)   |  |  |

|-------------------------|----|--------|-------|-------|-------|--------|-----------|--------------|--|--|

| \$ C00004               | 0  | A6     | A5    | A4    | A3    | A2     | A1 A0     | ( D7 ~ D0 )  |  |  |

| 2nd                     | 0  | 0      | 0     | 0     | 0     | 0      | 0 0       | ( D15 ~ D8 ) |  |  |

| \$ C00004               | 0  | 0      | 0     | 1     | 0     | 0      | 0 0       | ( D7 ~ D0 )  |  |  |

| A6 ~ A0 : VSRAM address |    |        |       |       |       |        |           |              |  |  |

| Data                    |    |        |       |       |       | VS10   | VS9 VS8   | ( D15 ~ D8 ) |  |  |

| \$ C00000               | VS | 7 VS6  | 5 VS5 | 5 VS4 | VS3   | 3 VS2  | 2 VS1 VS0 | ( D7 ~ D0 )  |  |  |

|                         |    | VS10 - | VSO : | V qu  | antit | y of s | scroll    |              |  |  |

If you use word for data and valid in D15  $\sim$  D0. D15 - D0 are valid when we use word for data set. If the writes are byte wide, write the high byte to \$C00000 and the low byte to \$C00001. A long word wide access is equivalent to two sequential word wide accesses. Place the first data in D31 - D16 and the second data in D15 - D0. The date may be written sequentially; the address is incremented by the value of REGISTER #15 after every write, independent of whether the width is byte of word.

Note that A0 is used in the increment but not in address decoding, resulting in some interesting side-effects if writes are attempted at odd addresses.

For word wide reads from the VSRAM, use:

| lst<br>\$ C00004        | 0 0  | 0<br>A6 A | 0<br>5 A4 | 0<br>A3 | 0<br>A2 | 0 0<br>A1 A0 | ( D15 ~ D8 )<br>( D7 ~ D0 )       |  |  |  |  |

|-------------------------|------|-----------|-----------|---------|---------|--------------|-----------------------------------|--|--|--|--|

| 2nd [                   | 0 0  | 0         |           | 0       | 0       | 0 0          | ( D15 ~ D8 )                      |  |  |  |  |

| \$ C00004               | 0    | 0 0       |           | 0       | 0       | 0 0          | $(D13 \sim D8)$<br>$(D7 \sim D0)$ |  |  |  |  |

| A6 ~ A0 : VSRAM address |      |           |           |         |         |              |                                   |  |  |  |  |

| Data                    |      |           |           | 1       | VS10 V  | VS9 VS8      | ( D15 ~ D8 )                      |  |  |  |  |

| \$ C00000               | VS7  | VS6 VS    | 5 VS4     | VS3     | VS2     | VS1 VS0      | ( D7 ~ D0 )                       |  |  |  |  |

|                         | VS10 | ~ VSO     | : V qu    | uantity | y of s  | croll        |                                   |  |  |  |  |

#### \_ ACCESS TIMING \_

The CPU and CDP access CRAM, CRAM, and VSRAM using timesharing. Because the VDP is very busy during the active scan, the CPU accesses are limited. However, during vertical blanking the CPU may access the CDP continuously.

The number of permitted accesses by the CPU additionally depends on whether the screen is in 32 cell mode or 40 cell mode. Additionally the access size depends on the RAM type; a VRAM access is byte wide, but CRAM and CSRAM are word wide.

For example, in 32 cell mode, the CPU may access the VRAM 16 times during horizontal scan in a single line. Each access is a byte write, so this amounts to 2 words. However CRAM and CSRAM though sharing the 16 time limit, are word accesses so that 16 words may be written in a single line.

Although these is a four-word FIFO. if writes are done in a tight loop during active scan the FIFO will fill up and the CPU will eventually end up waiting to write.

The maximum wait times are:

| DISPLAY MODE | MAXIMUM WAITING TIME  |

|--------------|-----------------------|

| H 32 cell    | Approximate 5.96 µsec |

| H 40 cell    | Approximate 4.77 µsec |

As the CPU has unlimited access to the RAMs during vertical blanking, the wait case never arises.

#### \_ HV COUNTER \_

The HV counter's function is to give the horizontal and vertical location of the television beam. If the "M3" bit of REGISTER #0 is set, the HV counter will then freeze when trigger signal HL goes high, as well as triggering a level 2 interrupt.

| М3 | COUNTER LATCH MODE                       |  |  |  |  |  |  |  |

|----|------------------------------------------|--|--|--|--|--|--|--|

| 0  | COUNTER IS NOT LATCHED BY TRIGGER SIGNAL |  |  |  |  |  |  |  |

| 1  | COUNTER IS LATCHED BY TRIGGER SIGNAL     |  |  |  |  |  |  |  |

|    | M3: REGISTER # 0                         |  |  |  |  |  |  |  |

#### NON INTERLACE MODE

| \$ C00008 | VC7 | VC6  | VC5  | VC4  | VC3   | VC2   | VC1   | VC8   | ( | D15 | ~ | D8 | ) |

|-----------|-----|------|------|------|-------|-------|-------|-------|---|-----|---|----|---|

| \$ 00000  | HC  | 8 HC | 7 HC | 5 HC | 5 HC4 | 4 HC3 | B HC2 | 2 HC1 |   | D7  | ~ | D0 | ) |

#### INTERLACE MODE

| \$ C00008 | VC7 | VC6 | VC5 | VC4   | VC3   | VC2 | VC1  | VC8   | _ ( | D15 | ~ | D8 | ) |

|-----------|-----|-----|-----|-------|-------|-----|------|-------|-----|-----|---|----|---|

| Ş C00008  | HC8 | HC7 | HCe | 5 HC5 | 5 HC4 | HC3 | B HC | 2 HC1 | ) ( | D7  | ~ | D0 | ) |

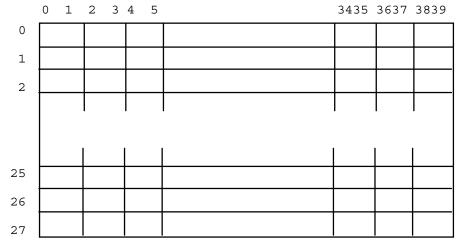

| V-COUNTER : VO | C7 ~ VC0     | H-COUNTER : HC8 ~ HC1     |

|----------------|--------------|---------------------------|

| DISPLAY MODE   | COUNTER DATA | DISPLAY MODE COUNTER DATA |

| V 28 CELL      | 0 ~ DFH      | H 32 CELL 0 ~ 7FH         |

| V 30 CELL      | 0 ~ EFH      | H 40 CELL 0 ~ 9FH         |

The counter only has eight bits each for H and V, so interlace mode and 40 cell (320 dots) modes present some problems. During interlace mode, the LSB of the vertical position is replaced by the new MSB. And the horizontal resolution problem is solved by ALWAYS dropping the LSB.

#### CAUTION:

As the HV counter's value is not valid during vertical blanking, check to be sure that it is active scan before using the value.

#### § 7 DMA TRANSFER

DMA (Direct Memory Access) is a high speed technique for memory accesses to the VRAM. CRAM and VSRAM. During DMA VRAM, CRAM and VSRAM occur at the fastest possible rate (please see the section on access timing). There are three modes of DMA access. as can be seen below. all of which may be done to VRAM or CRAM or VSRAM. The 68K is stopped during memory to VRAM/CRAM/VSRAM DMA, but the Z80 continues to run as long as it does not attempt access to the 68K memory space.

The DMA is quite fast during VBLANK. about double the tightest possible 68K Top's speed, but during active scan the speed is the same as a 68K loop.

Please note that after this point. VRAM is used as a generic term for  $\ensuremath{\mathsf{VRAM}}\xspace/\ensuremath{\mathsf{VSRAM}}\xspace.$

| DMD1 | DMD0 | DMA MODE                    | SIZE                |

|------|------|-----------------------------|---------------------|

| 0    | SA23 | A. MEMORY TO V-RAM          | WORD to BYTE(H)&(L) |

| 1    | 0    | B. VRAM FILL                | BYTE to BYTE        |

| 1    | 1    | C. VRAM COPY                | BYTE to BYTE        |

|      |      | DMD1, DMD0: REG #23 * DMD0= | SA23                |

Source address are \$00000-\$3FFFFF(ROM) and \$FF0000--\$FFFFFF(RAM) for memory to VRAM transfers. In the case of ROM to VRAM transfers, a hardware feature causes occasional failure of DMA unless the following two conditions are observed:

--The destination address write (to address \$C00004) must be a word write.

--The final write must use the work RAM.

There are two ways to accomplish this, by copying the DMA program into RAM or by doing a final "move.w ram address \$C00004"

#### \_ MEMORY TO VRAM \_

The function transfers data from 68K memory to VRAM, CRAM or VSRAM. During this DMA all 68K processing stops. The source address is \$000000-\$3FFFFF for ROM or \$FF0000-\$FFFFFF for RAM. The DMA reads are word wide. writes are byte wide for VRAM and word wide for CRAM and VSRAM. The destination is specified by:

| CD2 | CD1 | CD0 | MEMORY TYPE |

|-----|-----|-----|-------------|

| 0 0 | 1   |     | VRAM        |

| 0 1 | 1   |     | CRAM        |

| 1 0 | 1   |     | VSRAM       |

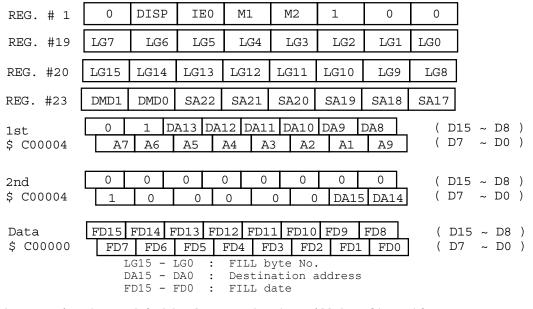

### Setting of DMA

(A) M1 (REG. #1)=1 : DMA ENABLE

(B) Increment No. set to #15 (normally 2)

(C) Transfer word No. set into #19, #20.

(D) Source address and DMA mode set into #21, #22, #23.

(E) Set the destination address.

(F)\*VDP gets the CPU bus.

(G)\*DMA start.

(H)\*VDP releases the CPU bus.

(I) M1 have to be 0 after confirmation of DMA finish : DMA DISABLED

DMA starts after (E). You must set M1=1 only during DMA otherwise we cannot guarantee the operation. Source address were increased with +2 and destination address increased with content of resister #15.

Content : of register. Register #1 has another bits.

| REG. #15         | INC7                                  | INC6    | INC5                      | INC4                                                   | INC3               | INC2         | INC1      | INC0       |                       |  |  |

|------------------|---------------------------------------|---------|---------------------------|--------------------------------------------------------|--------------------|--------------|-----------|------------|-----------------------|--|--|

|                  | INC7 ~                                | INC0    | : No.                     | of incr                                                | rement             |              |           |            |                       |  |  |

| REG. # 1         | 0                                     | DISP    | IE0                       | Ml                                                     | M2                 | 1            | 0         | 0          | ]                     |  |  |

| REG. #19         | LG7                                   | LG6     | LG5                       | LG4                                                    | LG3                | LG2          | LG1       | LG0        | ]                     |  |  |

| REG. #20         | LG15                                  | LG14    | LG13                      | LG12                                                   | LG11               | LG10         | LG9       | LG8        |                       |  |  |

| REG. #21         | SA8                                   | SA7     | SA6                       | SA5                                                    | SA4                | SA3          | SA2       | SA1        |                       |  |  |

|                  |                                       |         |                           |                                                        |                    |              |           |            |                       |  |  |

| REG. #23         | DMD1                                  | DMD0    | SA22                      | SA21                                                   | SA20               | SA19         | SA18      | SA17       |                       |  |  |

| 1st<br>\$ C00004 | CD1<br>A7                             |         |                           | 12 DA1<br>A4 A                                         | 1 DA10<br>.3 A2    | <u> </u>     | DA8<br>A9 | ( D<br>( D | 15 ~ D8 )<br>7 ~ D0 ) |  |  |

| 2nd<br>\$ C00004 | 0<br>1<br>LG15<br>SA23<br>DA15<br>CD2 | 3 - SA1 | 0<br>: No<br>: So<br>: De | 0 0<br>CD2<br>. of mo<br>urce ac<br>stinati<br>M selec | ldress<br>.on add: | d<br>(in 680 |           | ( D<br>( D | 15 ~ D8 )<br>7 ~ D0 ) |  |  |

\_ VRAM FILL

```

FILL mode fills with same data from free even VRAM address.

FILL for only VRAM.

```

How to set FILL(DMA).

- (A) M1 (REG. #1)=1 : DMA ENABLE

- (B) Increment No. set to #15 (normally 1).

- (B) Increment No. Set to #15 ((C) Fill size set to #19, #20.

- (D) DMA mode set to #23.(E) Destination address and FILL data set.

- (F) \*DMA start

- (G) M1=O after confirmation of finishing :DMA DISABLED

DMA starts at after (E). M1 should be 1 in the DMA transfer. otherwise we can't guarantee the operation. Destination address is incremented with register #15. VDP dose not asks bus open for CPU, but CPU cannot access VDP without PSG. HV counter and status. You can realize end of DMA, by DMA bit in status register.

Register setting. Register#1 has another bits.

| REG. #15                    | INC7 | INC6 | INC5 | INC4 | INC3 | INC2 | INC1 | INC0 |

|-----------------------------|------|------|------|------|------|------|------|------|

| INC7 - INC0 : Increment No. |      |      |      |      |      |      |      |      |

STATUS

| * | *  |     |   | * |   | *   |   | *    | *  | F | MPT | F | ULL |   |

|---|----|-----|---|---|---|-----|---|------|----|---|-----|---|-----|---|

| F | SC | DVR |   | С |   | ODI | ) | DT3  | VB |   | HB  | 3 | PAI | 5 |

|   | DM | A   | : | 1 | - | DMA |   | BUSY |    |   |     |   |     |   |

\* : Not care

When setting 1st and 2nd by long word. 1st will be D31 - D16 and 2nd, D15 - D0.

# 1 TERM: FILL data are word; register #15=1

### a. V-RAM address is even.

- (A) First, low side of FILL data are written in V-RAM address.

- (B) Second, upper side of FILL data are written in V-RAM+1.

(C) And, V-RAM address is added register #15, written upper side FILL data in V-RAM at next each step.

## b. V-RAM address is odd.

- (D)  $\,$  First, upper side of Fill data are written in

- V-RAM address-1.

- (E) Second, low side of Fill data are written in V-RAM.(F) Same as (C).

| • VRAM  | address is | even: | •VRAM address | is  | odd; |    |     |

|---------|------------|-------|---------------|-----|------|----|-----|

| ADD     | (A) Ev     | en    | ADD-1         |     | (D)  | Εv | en  |

| ADD+1 ( | 3) (C)     | Odd   | ADD           |     | (E)  |    | Odd |

| ADD+2 ( | C)         |       | ADD+1 (       | ſ   | )    |    |     |

| ADD+3 ( | C)         |       | ADD+2 (       | 5   | )    |    |     |

| ADD+4 ( | C)         |       | ADD+3 (       | ī.  | )    |    |     |

| ADD+5 ( | C)         |       | ADD+4 (       | ſ.  | )    |    |     |

| ADD+6 ( | C)         |       | ADD+5 (       | Гт. | )    |    |     |

| ADD+7   |            |       | ADD+6         |     | (F)  |    |     |

|         |            |       | ADD+7         |     |      |    |     |

\* You must rewrite data (C) into ADD+1 after write data (B).

2. TERM: FILL data are word; resister #15=2

| •VRAM addre | ss=even     |      | • VRAM | address= |          |       |

|-------------|-------------|------|--------|----------|----------|-------|

| ADD         | (A)lower E  | v en |        | ADD-1    | (D)upper | lv en |

| ADD+1       | (B)upper Do | d d  |        | ADD      | (E)lower | )d d  |

| ADD+2 (     | C )lower    |      |        | ADD+1    |          |       |

| ADD+3 u     | p per       |      |        | ADD+2    | (F)upper |       |

| ADD+4 (     | C )lower    |      |        | ADD+3    | lower    |       |

| ADD+5 u     | o per       |      |        | ADD+4    | (F)upper |       |

| ADD+6 (     | C )lower    |      |        | ADD+5    | lower    |       |

| ADD+7 u     | o per       |      |        | ADD+6    | (F)upper |       |

| _           |             |      |        | ADD+7    | lower    |       |

# 3. TERM: Fill data are byte.

a. V-RAM address is even.

(A) = (B) = (C) = BYTE \* DATA

b. V-RAM address is odd.

(D) = (E) = (F) = BYTE \* DATA

\_ VRAM COPY \_

This function dose copy from source address to destination address by number of COPY byte.

DMA setting

- (A) M1 (REG. #1) = 1 : DMA ENABLE

(B) Number of copy bytes in #19 #1

- Number of copy bytes in #19. #20

- (C) Source address and DMA mode in #23.

- (D) Destination address set.(E) \*DMA transfer

- (F) After confirming DMA finish :M1=O:DMA DISABLED

DMA starts when (D) above is finished. Apply M1=1 only during DMA transfer. In other cases, if M1=1 is set, there is no guaranty that it will function correctly. At the time of DMA transfer, the destination address is incremented by the set value of REG. #15. During DMA transfer. although the VDP does not require CPU to make a bus available, no access is possible from CPU to VDP except for PSG, HV counter. STATUS READ. DMA transfer finish can be recognized by referring to the STATUS REGISTER's DMA bit.

### Example: With TRANSFER BYTE=3 at the time of VRAM COPY

\* CAUTION

In the case of VRAM COPY, "read from VRAM" and "write to VRAM" are repeated per byte. Therefore, when the SOURCE AREA and TRANSFER AREA are over lapped, the transfer may not be performed correctly.

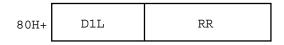

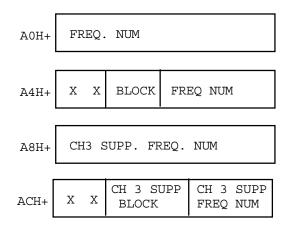

The attenuators are set for the four channels by writing the following bytes to I/O location  $\Fi$ :

| Tone Generator #1: | 1 ( | 0 0   | - | A3 | A2 | A1 | A0 |

|--------------------|-----|-------|---|----|----|----|----|

| Tone Generator #2: | 1 ( | ) 1 : |   | A3 | A2 | A1 | A0 |

| Tone Generator #3: | 1 : | . 0 : | - | A3 | A2 | A1 | A0 |

| Noise Generator:   | 1 : |       |   | A3 | A2 | A1 | A0 |

# EXAMPLE

..When the Mk3 is powered on, the following code is executed:

| LD     | HL,CLRTB   | ; | clear table      |

|--------|------------|---|------------------|

| LD     | C, PSG_PRT | ; | psg port is \$7F |

| LD     | в,4        | ; | load four bytes  |

| OTIR   |            | ; | write them       |

| (etc.) |            |   |                  |

CLTB defb \$9F,\$BF,\$DF,\$FF

This code turns the four sound channels off. It's a good idea to also execute this code when the PAUSE button is pressed, so that the sound does not stay on continuously for the pause interval.

REGISTER are as follows. REGISTER #1 includes bits set for purposes other than DMA. Therefore, pay careful attention in this regard.

| REG. #15          | INC7     | INC6                          | INC5   | INC4                          | INC3            | INC2      | INC1       | INCO                        |  |  |  |

|-------------------|----------|-------------------------------|--------|-------------------------------|-----------------|-----------|------------|-----------------------------|--|--|--|

|                   | INC7 ~   | INC0                          | : Incr | ement N                       | 10.             |           |            |                             |  |  |  |

| STATUS            | *        | *                             | *      | * *                           | *               | EMPT      | FULL       |                             |  |  |  |

| SIAIUS            | F        | SOVR                          |        |                               | VB HI           | B DMA     | PAL        |                             |  |  |  |

| DMA : 1: DMA BUSY |          |                               |        |                               |                 |           |            |                             |  |  |  |

| REG. # 1          | 0        | DISP                          | IE0    | Ml                            | M2              | 1         | 0          | 0                           |  |  |  |

| REG. #19          | LG7      | LG6                           | LG5    | LG4                           | LG3             | LG2       | LG1        | LG0                         |  |  |  |

| REG. #20          | LG15     | LG14                          | LG13   | LG12                          | LG11            | LG10      | LG9        | LG8                         |  |  |  |

| REG. #21          | SA7      | SA6                           | SA5    | SA4                           | SA3             | SA2       | SA1        | SA0                         |  |  |  |

|                   |          |                               |        |                               |                 |           |            |                             |  |  |  |

| REG. #23          | 1        | 1                             | 0      | 0                             | 0               | 0         | 0          | 0                           |  |  |  |

| lst<br>\$ C00004  | 0<br>DA7 |                               |        | 12 DA1<br>DA4 D               | 1 DA10<br>A3 DA | · · · · · | DA8<br>DA0 | ( D15 ~ D8 )<br>( D7 ~ D0 ) |  |  |  |

| 2nd               | 0        | 0                             | 0      | 0 0                           | 0               | 0         | 0          | ( D15 ~ D8 )                |  |  |  |

| \$ C00004         | 1        | 1                             | 0      | 0                             | 0 0             | ) DA15    | 5 DA14     | ( D7 ~ D0 )                 |  |  |  |

|                   | SA23     | 5 - LG0<br>8 - SA1<br>5 - DAO | : So   | mber of<br>urce ac<br>stinati | ldress          | -         |            |                             |  |  |  |

When setting 1st and 2nd by long word, 1st will be D31 - D16 and 2nd, D15 - D0.

## \_ DMA TRANSFER CAPACITY \_

Transfer quantity varies depending on the DISPLAY MODE as follows:

| DMA MODE  | DISPLAY MODE | SCREEN SCANNING                           | TRANSFER BYTES<br>PER LINE |

|-----------|--------------|-------------------------------------------|----------------------------|

| MEMORY    | H32 CELL     | DURING EFFECTIVE SCREEN<br>DURING V BLANK | 16 Bytes<br>167 Bytes      |

| TO VRAM   | H40 CELL     | DURING EFFECTIVE SCREEN<br>DURING V BLANK | 18 Bytes<br>205 Bytes      |

| VRAM FILL | H32 CELL     | DURING EFFECTIVE SCREEN<br>DURING V BLANK | 15 Bytes<br>166 Bytes      |

|           | H40 CELL     | DURING EFFECTIVE SCREEN<br>DURING V BLANK | 17 Bytes<br>204 Bytes      |

| VRAM COPY | H32 CELL     | DURING EFFECTIVE SCREEN<br>DURING V BLANK | 8 Bytes<br>83 Bytes        |

|           | H40 CELL     | DURING EFFECTIVE SCREEN<br>DURING V BLANK | 9 Bytes<br>102 Bytes       |

In the MEMORY TO VRAM. in the case where CRAM and VSRAM are the destinations, number of words (not byte) should apply. One line during V BLANK allows for data transfer to all the address of CRAM and VSRAM.

Note that when calculating, the transfer quantity in one screen (1/60 sec) varies depending on the number of LINES during V BLANK (refer to DISPLAY MODE) in the case of NTSC (video signal) and PAL systems.

| DISPLAY MODE     | No. of Horizontal line |

|------------------|------------------------|

| V 28 CELL (NTSC) | 36                     |

| V 28 CELL (PAL)  | 87                     |

| V 30 CELL (PAL)  | 71                     |

Where REGISTER #1 DISP=O, 1, e.. when on-screen display is not made, the TRANSFER quantity is the same as TRANSFER BYTES PER LINE during BLANKING.

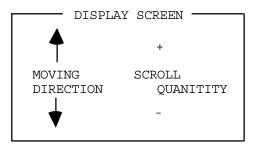

## §8 SCROLLING SCREEN

SCROLL "A" PATTERN NAME TABLE BASE ADDRESS

There are two different scroll screens, i.e. A and B which separately can scroll vertically and horizontally on a basis of a one dot unit. In the horizontal direction, scrolling overall or based on a one cell unit or one line unit can be selected. And in the vertical direction. scrolling overall or in. a two cell unit can be selected. Also, the scroll screen size can be changed on a basis of a 32 cell unit.

| SCROLL SCREEN            |

|--------------------------|

|                          |

| EFFECTIVE DISPLAY SCREEN |

|                          |

|                          |

|                          |

|                          |

|                          |

|                          |

For the scrolling screen display, the following REGISTER setting and VRAM area are required.

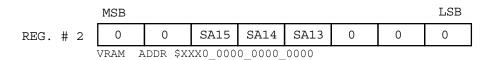

| REG.                                                                                                                                   | # 2    | 0        | 0        | SA15    | SA14     | SA13 | 0    | 0        | 0    |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------|--------|----------|----------|---------|----------|------|------|----------|------|--|--|--|

| SCROLL                                                                                                                                 | "B" I  | ATTERN   | NAME T   | ABLE BA | SE ADDE  | RESS |      |          |      |  |  |  |

| REG.                                                                                                                                   | # 4    | 0        | 0        | 0       | 0        | 0    | SB15 | SB14     | SB13 |  |  |  |

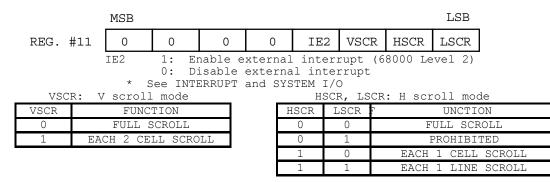

| MODE SET REGISTER No. 3                                                                                                                |        |          |          |         |          |      |      |          |      |  |  |  |

| REG.                                                                                                                                   | #11    | 0        | 0        | 0       | 0        | IE2  | VSCR | HSCR     | LSCR |  |  |  |

| MODE SET REGISTER No. 4                                                                                                                |        |          |          |         |          |      |      |          |      |  |  |  |

| REG.                                                                                                                                   | #12    | RS0      | 0        | 0       | 0        | S/TE | LSM1 | LSM0     | RS1  |  |  |  |

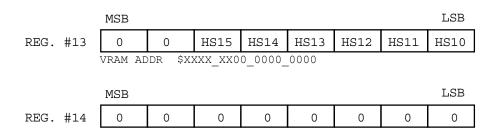

| H SCRO                                                                                                                                 | LL DAT | TA TABLE | E BASE 2 | ADDRESS | <u> </u> |      |      |          |      |  |  |  |

| REG.                                                                                                                                   | #13    | 0        | 0        | HS15    | HS14     | HS13 | HS12 | HS11     | HS10 |  |  |  |

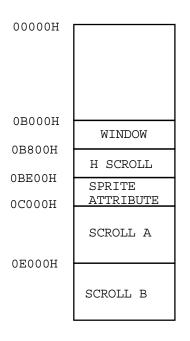

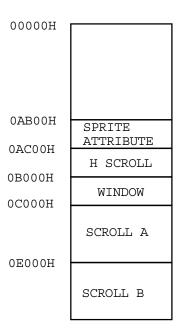

| SCROLL                                                                                                                                 | SIZE   |          |          |         |          |      |      |          |      |  |  |  |